# Noise Relations for Parallel Connected Transistors\*

W. MARSHALL LEACH, JR., AES Fellow

Georgia Institute of Technology, School of Electrical and Computer Engineering, Atlanta, GA 30332-0250, USA

The mean-square equivalent noise input voltage is calculated for an amplifier input stage for the case where the stage consists of a number of identical devices connected in parallel. The devices that are considered are the BJT and the MOSFET. The effect on noise of the number of devices and the bias current in each device is investigated.

## **0 INTRODUCTION**

A technique of low-noise amplifier design is to realize the input stage with a number of identical active devices connected in parallel [1]-[7]. If the signal outputs of the devices are correlated and the noise outputs are not correlated, the signal-to-noise ratio (SNR) is improved by 3 dB each time the number of devices is doubled. However, this is true only if the thermal noise generated by the resistance of the signal source at the input is negligible. If not, there is a correlated noise component at the output of each device due to the source noise. This component causes the improvement in SNR for the source and amplifier in combination to be less than the 3-dB upper bound when the number of devices is doubled. In this case there is an optimum number of devices that maximizes the SNR which is dependent on the source resistance. Any number greater than this optimum causes a decrease.

This engineering report investigates the noise performance of amplifier input stages consisting of parallel bipolar junction transistors (BJTs) and parallel metal oxide semiconductor field effect transistors (MOSFETs). The noise is considered to be a minimum when the SNR is a maximum. It is shown that the parallel connection of BJTs biased at a fixed total current only results in a reduction in the thermal noise generated by the base spreading resistance. The optimum number of parallel BJTs is obtained which maximizes the SNR when the current per device is held constant. In addition, the optimum bias current per BJT is obtained which maximizes the SNR for a fixed number of devices. It is shown that

the parallel connection of N identical MOSFETs biased at a fixed total current has the same noise performance as a single MOSFET having an effective channel width that is N times larger.

The notation used in the analysis is as follows. A dc bias value is denoted by an uppercase letter with an uppercase subscript, such as  $I_C$ ; a small-signal value is denoted by a lowercase letter with a lowercase subscript, such as  $v_n$ ; and a mean-square value is denoted by a bar over the square of the variable, such as  $v_n^2$ . The mean-square value of a variable is the square of its rms value. Circuit symbols for independent signal sources are round. Symbols for dependent sources are diamond shaped. Symbols for noise sources are square.

#### 1 PARALLEL CONNECTED BJTs

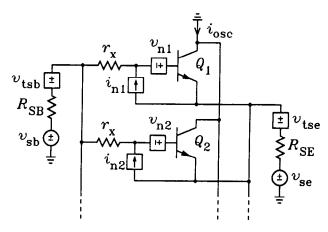

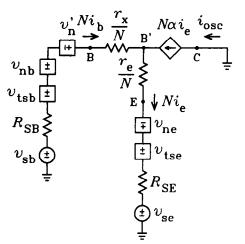

Fig. 1 shows the signal circuit of the input stage of an amplifier consisting of N identical BJTs connected in parallel. Each is represented by its  $v_n - i_n$  noise model, where  $v_{nj}$  and  $i_{nj}$  represent, respectively, the input noise voltage and current for the jth device. There are two signal sources,  $v_{sb}$  and  $v_{se}$ . Each is modeled as a Thévenin source, where  $v_{tsb}$  and  $v_{tse}$  are the thermal noise voltages generated by the source resistances  $R_{SB}$  and  $R_{SE}$ , respectively. The circuit is a common-emitter (CE) amplifier if  $v_{se} = 0$  and a common-base (CB) amplifier if  $v_{sb} = 0$ . By analyzing the circuit with the two sources, the noise for both configurations can be calculated without repeating the analysis. It is shown that the equivalent noise input voltage can be considered to be in series with either input source.

The base spreading resistance  $r_x$  of each BJT in Fig. 1 is shown as an external resistor. This resistor is considered to be noiseless in the model, for its noise is con-

<sup>\*</sup> Manuscript received 1998 August 24; revised 1999 February 2.

tained in  $v_n$ . The noise voltage and the noise current in the BJT noise model are given by [7]

$$v_{\rm n} = v_{\rm tx} + i_{\rm shc} \frac{V_{\rm T}}{I_{\rm C}} \tag{1}$$

$$i_{\rm n} = i_{\rm shb} + i_{\rm fb} + \frac{i_{\rm shc}}{\beta} \,. \tag{2}$$

In these equations,  $v_{\rm tx}$  is the thermal noise generated by  $r_{\rm x}$ ,  $i_{\rm shc}$  is the shot noise in the collector bias current  $I_{\rm C}$ ,  $i_{\rm shb}$  is the shot noise in the base bias current  $I_{\rm B}$ ,  $i_{\rm fb}$  is the flicker noise in the base bias current,  $\beta = I_{\rm C}/I_{\rm B}$  is the current gain, and  $V_{\rm T} = kT/q$  is the thermal voltage, with k Boltzmann's constant, T the absolute temperature, and q the electronic charge.

The noise sources have the following mean-square values [6]-[8]:

$$\overline{v_{\rm tsb}^2} = 4kTR_{\rm SB}\Delta f \tag{3}$$

$$\overline{v_{\rm tse}^2} = 4kTR_{\rm SE}\Delta f \tag{4}$$

$$\overline{v_{\rm tx}^2} = 4kTr_{\rm x}\Delta f \tag{5}$$

$$\overline{i_{\rm shc}^2} = 2qI_{\rm C}\Delta f \tag{6}$$

$$\overline{i_{\rm shb}^2} = 2qI_{\rm B}\Delta f \tag{7}$$

$$\overline{i_{\rm fb}^2} = K_{\rm f} I_{\rm B} \frac{\Delta f}{f} \tag{8}$$

where  $\Delta f$  is the frequency band in hertz over which the noise is measured,  $K_f$  is the flicker noise coefficient, and f is the frequency in hertz. It is commonly assumed that the sources are independent, that is, not correlated.

The analysis is simplified if all transistor noise sources are represented as voltage sources in series with  $R_{\rm SB}$  and  $R_{\rm SE}$ . To put the circuit into this form, the first step is to move the upper lead of each  $i_{\rm n}$  source from the right node of its corresponding  $r_{\rm x}$  to the left node of  $r_{\rm x}$ . This requires changing the value of the  $v_{\rm nj}$  sources to  $v'_{\rm nj}$ , given by

$$v'_{\mathbf{n}j} = v_{\mathbf{n}j} + i_{\mathbf{n}j}r_{\mathbf{x}}. \tag{9}$$

Next replace each  $i_n$  source with two series sources, each having the value  $i_n$ , with the common node between the two grounded. All currents in the transistors are independent of these source transformations.

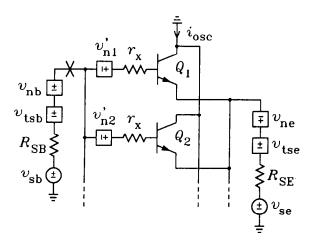

The next step is to replace the circuits seen looking out of the parallel connected bases and emitters with Thévenin equivalent circuits and to reverse the order of each  $v'_n$  and  $r_x$  in series with the bases. The resulting circuit is shown in Fig. 2, where  $v_{nb}$  and  $v_{ne}$  are given by

$$v_{\rm nb} = R_{\rm SB} \sum_{j=1}^{N} i_{nj} \tag{10}$$

$$v_{\rm ne} = R_{\rm SE} \sum_{j=1}^{N} i_{\rm nj} \,. \tag{11}$$

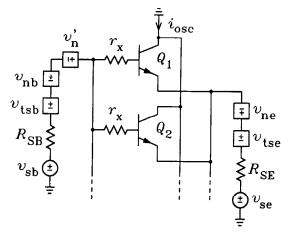

The last step is to replace the  $v'_{nj}$  sources with a single source equal to the common-mode value of the N sources at the position  $\times$  in Fig. 2. The circuit is shown in Fig. 3, where  $v'_n$  is given by

$$v'_{n} = \frac{1}{N} \sum_{j=1}^{N} v'_{nj} = \frac{1}{N} \sum_{j=1}^{N} (v_{nj} + i_{nj} r_{x}).$$

(12)

Because the latter step is not obvious, a simple proof is presented for the case N = 3. It is straightforward to

Fig. 1. Signal circuit for parallel connected BJT stage.

Fig. 2. BJT circuit with  $i_{nj}$  sources removed.

Fig. 3. BJT circuit with  $v'_{nj}$  sources removed.

extend the proof for other values of N. For simplicity, let the three noise voltage sources be represented by x, y, and z. We can write x = a + b + c, y = a - b + d, and z = a - c - d, where a = (x + y + z)/3, b = (x - y)/3, c = (x - z)/3, and d = (y - z)/3. Because of linearity, superposition of a, b, c, and d can be used to obtain the total response of the circuit. When a alone is active, the three sources are equal and the response of the circuit is the same as for a single source a at the position  $\times$  in Fig. 2. When b alone is active,  $Q_1$  and  $Q_2$  are driven differentially and the collector output currents cancel. The same happens between  $Q_1$  and  $Q_3$  when c is active and between  $Q_2$  and  $Q_3$  when d is active. This completes the proof.

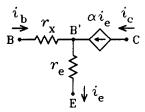

The T model of the BJT is shown in Fig. 4, where  $r_e = V_T/I_E$  is the intrinsic emitter resistance,  $I_E$  is the emitter bias current, and  $\alpha = I_C/I_E$ . When the model is substituted for the transistors in the circuit of Fig. 3, it follows by symmetry that all transistors have the same currents and the same voltages at the B' nodes. Therefore, the T models can be combined in parallel to form the final circuit of Fig. 5. The following loop equation on be written:

The first term in this equation arises from the thermal noise generated by  $R_{\rm SB}$ ,  $r_{\rm x}$ , and  $R_{\rm SE}$ . The second term arises from the shot noise and flicker noise in  $I_{\rm B}$ . The third term arises from the shot noise in  $I_{\rm C}$ .

The SNR of the stage is given by

$$SNR = \frac{\overline{v_s^2}}{v_{pi}^2}$$

(18)

where  $\overline{v_s^2} = \overline{v_{sb}^2}$  for the CE configuration and  $\overline{v_s^2} = \overline{v_{se}^2}$  for the CB configuration. It follows that the SNR is maximized when  $\overline{v_{ni}^2}$  is minimized. It can be concluded from Eq. (17) that a first step in minimizing the noise is to make  $R_{SE}$  as small as possible for the CE configuration and  $R_{SB}$  as small as possible for the CB configuration. For each configuration it is assumed that the source resistance is fixed and cannot be varied. For example, the source resistance might be the output resistance of a low-level transducer such as a microphone or a tape head.

Eq. (17) is valid only at frequencies where the effects

$$v_{\rm sb} - v_{\rm se} + v_{\rm tsb} - v_{\rm tse} + v_{\rm nb} + v_{\rm ne} + v'_{\rm n} = Ni_{\rm b} \left( R_{\rm SB} + \frac{r_{\rm x}}{N} \right) + Ni_{\rm e} \left( \frac{r_{\rm e}}{N} + R_{\rm SE} \right).$$

(13)

Because  $i_b = (1 - \alpha) i_e$ , it follows that  $i_c$  can be solved for to obtain

$$i_{e} = \frac{v_{sb} - v_{se} + v_{tsb} - v_{tse} + v_{nb} + v_{ne} + v'_{n}}{N(1 - \alpha)(R_{SB} + r_{x}/N) + N(r_{e}/N + R_{SE})}.$$

(14)

The short-circuit output current is given by  $i_{\rm osc} = N\alpha i_{\rm e}$ . It follows that the equivalent noise voltage  $v_{\rm ni}$  in series with either  $v_{\rm sb}$  or  $v_{\rm se}$ , which generates the same noise current in  $i_{\rm osc}$  as all noise sources in the circuit, is given by

$$v_{ni} = v_{tsb} - v_{tse} + v_{nb} + v_{ne} + v'_{n}$$

$$= v_{tsb} - v_{tse} + \left(R_{SB} + \frac{r_{x}}{N} + R_{SE}\right) \sum_{j=1}^{N} i_{nj} + \frac{1}{N} \sum_{j=1}^{N} v_{nj}.$$

(15)

This is the equivalent noise input voltage for both the CE and the CB configurations.

With the aid of Eqs. (1) and (2), the equation for  $v_{ni}$  can be reduced to

of the BJT base-emitter diffusion capacitance  $c_{\pi}$  and the collector-base depletion capacitance  $c_{\mu}$  can be neglected. With devices in parallel, these capacitors combine in parallel in the equivalent circuit. This can result in a degradation in the high-frequency performance or in the stability of the circuit. Because  $c_{\pi}$  is proportional to  $I_{\rm C}$ , the parallel combination of these capacitors does not change with N if the total stage current is held constant.

#### 1.1 Noise Factor

The noise factor of an amplifier is given by

$$F = \frac{\overline{v_{\text{ni}}^2}}{\overline{v_{\text{n}}^2}} = 1 + \frac{\overline{v_{\text{n}}^2} + 2\rho \sqrt{\overline{v_{\text{n}}^2}} \sqrt{\overline{i_{\text{n}}^2}} R_{\text{S}} + \overline{i_{\text{n}}^2} R_{\text{S}}^2}{4kTR_{\text{S}}\Delta f}$$

(19)

where  $v_{\rm ni} = v_{\rm ts} + v_{\rm n} + i_{\rm n}R_{\rm S}$  is the equivalent noise input voltage,  $v_{\rm ts}$  is the thermal noise generated by the source resistance  $R_{\rm S}$ ,  $v_{\rm n}$  is the input noise voltage,  $i_{\rm n}$  is the input noise current, and  $\rho$  is the correlation coeffi-

$$v_{\text{ni}} = v_{\text{tsb}} - v_{\text{tsc}} + \frac{1}{N} \sum_{j=1}^{N} v_{\text{tx}j} + \left( R_{\text{SB}} + \frac{r_{\text{x}}}{N} + R_{\text{SE}} \right) \sum_{j=1}^{N} (i_{\text{shb}j} + i_{\text{fb}j}) + \left( \frac{R_{\text{SB}} + r_{\text{x}}/N + R_{\text{SE}}}{\beta} + \frac{V_{\text{T}}}{NI_{\text{C}}} \right) \sum_{j=1}^{N} i_{\text{shc}j}. \quad (16)$$

This can be converted to a mean-square voltage to obtain

$$\overline{v_{\text{ni}}^2} = 4kT\left(R_{\text{SB}} + \frac{r_{\text{x}}}{N} + R_{\text{SE}}\right)\Delta f + \left(R_{\text{SB}} + \frac{r_{\text{x}}}{N} + R_{\text{SE}}\right)^2 \left(2qNI_{\text{B}}\Delta f + \frac{K_{\text{f}}NI_{\text{B}}\Delta f}{f}\right) + \left(\frac{R_{\text{SB}} + r_{\text{x}}/N + R_{\text{SE}}}{\beta} + \frac{V_{\text{T}}}{NI_{\text{C}}}\right)^2 2qNI_{\text{C}}\Delta f.$$

(17)

cient between  $v_n$  and  $i_n$ .

The value of  $R_S$  which minimizes F is called the optimum source resistance  $R_{SO}$ . It is obtained by setting  $dF/dR_S = 0$  and solving for  $R_S$ , and is given by

$$R_{\rm SO} = \sqrt{\frac{\overline{v_{\rm n}^2}}{\overline{i_{\rm n}^2}}}.$$

(20)

The corresponding value of F is called the optimum noise factor and is given by

$$F_{\text{opt}} = 1 + \frac{\overline{v_{\text{n}}^2}(1+\rho)}{2kTR_{\text{SO}}\Delta f}.$$

(21)

To solve for  $R_{\rm SO}$  for the parallel BJT stage, a CE configuration is assumed so that  $R_{\rm SB}$  is the source resistance and  $v_{\rm tsb}$  is the thermal noise generated by the source. In this case, the equivalent noise input voltage  $v_{\rm ni}$  is written

$$v_{\rm ni} = v_{\rm tsb} + v_{\rm n} + i_{\rm n}R_{\rm SB}. \tag{22}$$

When this is compared to Eq. (15), it follows that the input noise voltage and current are given by

$$v_{\rm n} = -v_{\rm tse} + \left(\frac{r_{\rm x}}{N} + R_{\rm SE}\right) \sum_{j=1}^{N} i_{\rm nj} + \frac{1}{N} \sum_{j=1}^{N} v_{\rm nj}$$

(23)

$$i_{\rm n} = \sum_{j=1}^{N} i_{\rm nj} \,. \tag{24}$$

Fig. 4. T model of BJT.

Fig. 5. Final BJT circuit.

These can be converted into mean-square values and substituted into Eq. (20) to obtain

$$R_{SO} = \left[ \left( \frac{r_{x}}{N} + R_{SE} \right)^{2} + \frac{2\beta V_{T} (r_{x} + R_{SE} + V_{T}/2I_{C})}{N^{2}I_{C}(1 + 1/\beta)} \right]^{1/2}$$

(25)

where it is assumed that the frequency is high enough so that flicker noise can be neglected. If  $R_S \neq R_{SO}$ , resistors should never be added in series or in parallel with the source to make the effective source resistance equal to  $R_{SO}$ . Although this minimizes F, the SNR is decreased. This is called the noise factor fallacy.

#### 1.2 Constant Stage Current

If the total bias current in the parallel stage is held constant, the bias current per device is proportional to 1/N. It follows that  $NI_{\rm C}$  and  $NI_{\rm B}$  are constant in Eq. (17). In this case, the total noise caused by base current shot and flicker noise and collector current shot noise is constant. The only reduction in  $\overline{v_{\rm ni}^2}$  that can be achieved by increasing N is in the thermal noise generated by  $r_{\rm x}$ . If  $R_{\rm SB} + R_{\rm SE} >> r_{\rm x}/N$ , an increase in N results in little or no improvement in the noise.

If N is made too large, the decrease in  $I_C$  can affect the performance of the BJT if  $I_C$  becomes too small. If the devices become starved for collector current, the current gain  $\beta$  may drop. This can cause the noise performance to deteriorate.

## 1.3 Constant Device Current

If  $R_{\rm SB}=R_{\rm SE}=0$  and  $I_{\rm C}$  is held constant, the total bias current for the stage is proportional to N. It follows from Eq. (17) that  $\overline{v_{\rm ni}^2} \propto 1/N$ . Thus the noise is reduced by 3 dB each time N is doubled. For  $R_{\rm SB}>0$  or  $R_{\rm SE}>0$ , the noise is reduced by less than 3 dB when N is doubled.

The power dissipated in the stage is proportional to the square of the total bias current. It follows that the power increases as  $N^2$  for constant device current. Thus a limitation on the maximum acceptable power dissipation translates into a limit on N.

## 1.4 Optimum N

If  $I_C$  is fixed, there is a value of N that minimizes the noise. When N is increased above this value, the noise increases. The optimum value of N that minimizes  $\overline{v_{ni}^2}$  can be obtained by setting  $d\overline{v_{ni}^2}/dN=0$  and solving for N. It is given by

$$N_{\text{opt}} = \frac{\beta V_{\text{T}}}{I_{\text{C}}(R_{\text{SB}} + R_{\text{SE}})} \sqrt{\left(1 + \frac{I_{\text{C}}r_{\text{x}}}{\beta V_{\text{T}}}\right)^2 - \frac{\beta}{1 + \beta}} \quad (26)$$

where it is assumed that the frequency is high enough so that the flicker noise can be neglected. For this value of N it is straightforward to show that the minimized mean-square noise voltage is given by

$$\overline{v_{\rm ni(min)}^2} = 4kT(R_{\rm SB} + R_{\rm SE}) \, \Delta f \left( 1 + \frac{1}{\beta} \right) \left( 1 + \frac{I_{\rm C}}{\beta V_{\rm T}} \left[ r_{\rm x} + N_{\rm opt} \left( R_{\rm SB} + R_{\rm SE} \right) \right] \right). \tag{27}$$

LEACH ENGINEERING REPORTS

For  $N \neq N_{\text{opt}}$ , it can be shown that the expression for  $\overline{v_{\text{ni}}^2}$  can be written

$$\overline{v_{\text{ni}}^2} = \overline{v_{\text{ni(min)}}^2} \left[ 1 + \frac{0.5(N/N_{\text{opt}} + N_{\text{opt}}/N) - 1}{1 + \sqrt{1 + \beta}} \right].$$

(28)

This equation shows that  $\overline{v_{\text{ni}}^2}$  is the same for  $N = rN_{\text{opt}}$  as it is for  $N = N_{\text{opt}}/r$ , where r is any positive constant.

## 1.5 Optimum Bias Current

If N is held constant and  $I_{\rm C}$  is varied, the value of  $I_{\rm C}$  that minimizes  $\overline{v_{\rm ni}^2}$  can be obtained by setting  ${\rm d}\overline{v_{\rm ni}^2}/{\rm d}I_{\rm C}=0$  and solving for  $I_{\rm C}$ . It is given by

$$I_{\text{C(opt)}} = \frac{\beta V_{\text{T}}}{[N(R_{\text{SB}} + R_{\text{SE}}) + r_{\text{x}}]\sqrt{1+\beta}}$$

(29)

where it is assumed that the frequency is high enough so that the flicker noise can be neglected. In this case, the minimized mean-square voltage is given by

$$\overline{v_{\text{ni(min)}}^2} = 4kT \left( R_{\text{SB}} + R_{\text{SE}} + \frac{r_{\text{x}}}{N} \right) \Delta f \frac{\sqrt{1+\beta}}{\sqrt{1+\beta} - 1}.$$

(30)

For  $I_C \neq I_{C(opt)}$ , the expression for  $\overline{v_{ni}^2}$  can be put into the form

$$\overline{v_{\text{ni}}^2} = \overline{v_{\text{ni(min)}}^2} \left( 1 + \frac{0.5[I_C/I_{\text{C(opt)}} + I_{\text{C(opt)}}/I_C] - 1}{1 + \sqrt{1 + \beta}} \right).$$

(31)

This equation shows that  $\overline{v_{ni}^2}$  is the same for  $I_C = rI_{C(opt)}$  as it is for  $I_C = I_{C(opt)}/r$ , where r is any positive constant.

#### **2 PARALLEL CONNECTED MOSFETs**

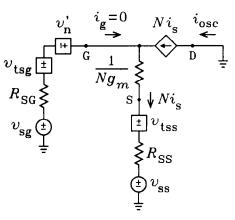

Fig. 6 shows the signal circuit of the input stage of an amplifier consisting of N identical MOSFETs connected in parallel. It is assumed that the body or bulk terminal of each device is connected to the source terminal. Each MOSFET is represented by its  $v_n$  noise model, where  $v_{nj}$  represents the input noise voltage for the jth

$v_{\text{tsg}} \stackrel{\bar{\downarrow}}{=} v_{\text{osc}}$   $v_{\text{n1}} \stackrel{\bar{\downarrow}}{=} v_{\text{osc}}$   $v_{\text{n2}} \stackrel{\bar{\downarrow}}{=} v_{\text{tss}}$   $v_{\text{sg}} \stackrel{\bar{\downarrow}}{=} v_{\text{ss}}$

Fig. 6. Signal circuit for parallel connected MOSFET stage.

device. Because the gate bias current is so minuscule in the MOSFET, there is no  $i_n$  noise source. There are two signal sources,  $v_{sg}$  and  $v_{ss}$ . For  $v_{ss} = 0$ , the configuration is a common-source (CS) amplifier. For  $v_{sg} = 0$ , it is a common-gate (CG) amplifier. The noise sources  $v_{tsg}$  and  $v_{tss}$  represent the thermal noise generated by the source resistances  $R_{SG}$  and  $R_{SS}$ , respectively.

It is assumed that the MOSFETs are biased in the saturation region. In this region the device bias voltages must satisfy  $V_{\rm DS} > V_{\rm GS} - V_{\rm TO}$ , where  $V_{\rm DS}$  is the drainto-source voltage,  $V_{\rm GS}$  is the gate-to-source voltage, and  $V_{\rm TO}$  is the device threshold voltage.

The input noise voltage in the MOSFET model is given by [6]-[9]

$$v_{\rm n} = \frac{i_{\rm td} + i_{\rm fd}}{g_{\rm m}} \tag{32}$$

where  $i_{td}$  is the thermal noise generated in the channel,  $i_{fd}$  is the flicker noise generated in the channel, and  $g_m$  is the transconductance. The latter is given by  $g_m = 2$   $\sqrt{KI_D}$ , where K is the transconductance parameter and  $I_D$  the drain bias current. The transconductance parameter is given by  $K = \mu_0 C_{ox} W/2L$ , where  $\mu_0$  is the average carrier mobility in the channel,  $C_{ox}$  is the gate oxide capacitance per unit area, W is the effective channel width, and L is the effective channel length.

With appropriate subscript changes, the mean-square values of  $v_{\rm tsg}$  and  $v_{\rm tss}$  are given by Eqs. (3) and (4). The mean-square values of the two noise currents in Eq. (32) are given by [6]-[9]

$$\overline{i_{\rm td}^2} = 4kT \left(\frac{2g_{\rm m}}{3}\right) \Delta f = \frac{16}{3} kT \sqrt{KI_{\rm D}} \Delta f \tag{33}$$

$$\overline{i_{\rm fd}^2} = \frac{K_{\rm f} I_{\rm D} \Delta f}{f L^2 C_{\rm ex}} \tag{34}$$

where  $K_f$  is the flicker noise coefficient. It is commonly assumed that the noise sources are independent.

The MOSFET circuit can be transformed into a circuit similar to that in Fig. 5. The transformation is similar to that for the BJT, with the exception that there are no  $i_n$  sources. The final circuit is given in Fig. 7, where the

Fig. 7. Final MOSFET circuit.

T model of the MOSFET is used. The noise voltage  $v'_n$  is given by

$$v_{\rm n}' = \frac{1}{N} \sum_{j=1}^{N} v_{\rm nj} = \frac{1}{N} \sum_{j=1}^{N} \frac{i_{\rm tdj} + i_{\rm fdj}}{g_{\rm m}}.$$

(35)

The following loop equation can be written for the circuit:

$$v_{sg} - v_{ss} + v_{tsg} - v_{tss} + v'_{n} = Ni_{s} \left( \frac{1}{Ng_{m}} + R_{SS} \right).$$

(36)

This equation can be solved for  $Ni_s$  to obtain

$$Ni_{s} = \frac{v_{sg} - v_{ss} + v_{tsg} - v_{tss} + v'_{n}}{1/Ng_{m} + R_{SS}}.$$

(37)

Because  $i_{\rm osc} = Ni_{\rm s}$ , it follows that the equivalent noise voltage in series with either  $v_{\rm sg}$  or  $v_{\rm ss}$  that generates the same noise in  $i_{\rm osc}$  is given by

$$v_{ni} = v_{tsg} - v_{tss} + v'_{n}$$

$$= v_{tsg} - v_{tss} + \frac{1}{N} \sum_{i=1}^{N} \frac{i_{tdj} + i_{fdj}}{g_{m}}.$$

(38)

This can be converted into a mean-square voltage to obtain

$$\overline{v_{\text{ni}}^2} = 4kT (R_{\text{SG}} + R_{\text{SS}}) \Delta f + \frac{4kT\Delta f}{3} \sqrt{\frac{2L}{\mu_0 C_{\text{ox}}(NW)(NI_{\text{D}})}} + \frac{K_f \Delta f}{2\mu_0 C_{\text{ox}}(NW) fL}.$$

(39)

The first term in Eq. (39) arises from the thermal noise generated by  $R_{SG}$  and  $R_{SS}$ . The second arises from the thermal noise generated in the channel. The third term arises from the flicker noise generated in the channel. The SNR is given by Eq. (18), where  $\overline{v_s^2} = \overline{v_{sg}^2}$  for the CS configuration and  $\overline{v_{sg}^2}$  and  $\overline{v_{sg}^2}$  for the CG configuration. The SNR is maximized when  $\overline{v_{ni}^2}$  is minimized.

#### 2.1 Constant Stage Current

It can be seen from Eq. (39) that  $\overline{v_{\text{ni}}^2}$  is a monotonically decreasing function of both N and  $I_{\text{D}}$ . Thus there is no optimum value for either which minimizes the noise. If the total bias current in the stage is held constant, the bias current per device is proportional to 1/N. In this case,  $NI_{\text{D}}$  is a constant and  $\overline{v_{\text{ni}}^2}$  is a function of the product NW. The thermal noise component decreases by 1.5 dB each time N is doubled while the flicker noise component decreases by 3 dB.

Because  $v_{ni}^2$  is a function of NW, it follows that increasing the width of a single device by a factor N has the same effect on the noise as connecting N devices in parallel. However, this conclusion must be considered to be an oversimplification due to the limitations of physical devices. For example, it ignores the issue of the effective series gate resistance. The resistance of the physically long and narrow polysilicon gate in a wide-

gate device can be significant. While the effective gate resistance is reduced by a factor of N when N devices are paralleled, this is not necessarily true for a single device of N times the width. In addition, the high-frequency response of the latter device is degraded by the distributed delay line formed by the gate resistance and capacitance.

#### 2.2 Constant Device Current

If  $R_{SG} = R_{SS} = 0$  and  $I_D$  is held constant, the total bias current in the stage is proportional to N. For this case, it follows from Eq. (39) that  $\overline{v_{ni}^2} \propto 1/N$ . Thus the noise is reduced by 3 dB each time N is doubled. For  $R_{SG} > 0$  or  $R_{SS} > 0$ , the thermal and flicker noise components both decrease by 3 dB each time N is doubled. However, the total noise decreases by less than 3 dB because the thermal noise generated by  $R_{SG}$  and  $R_{SS}$  is not a function of N. As with the BJT stage, the power dissipation increases as  $N^2$ .

#### **3 CONCLUSIONS**

The noise performance of an amplifier stage that consists of a number of devices in parallel is a function of both the number of devices and the total bias current of the stage. If the total bias current is held constant as the number of devices is varied, the noise varies differently than if the bias current per device is held constant. These

effects have been investigated here for the BJT and the MOSFET. For a constant total bias current it has been shown that the parallel connection of BJTs can only be used to decrease the noise generated by the BJT base spreading resistance. The decrease in noise achieved by the parallel connection of MOSFETs can be achieved by fabricating a single MOSFET with an effective gate width that is larger by a factor equal to the number of parallel devices.

## **4 REFERENCES**

- [1] E. A. Faulkner, "Optimum Design of Low-Noise Amplifiers," *Elec. Lett.*, vol. 2, pp. 426-427 (1960 Nov.).

- [2] T. K. Matsudaira, "Noise Behavior of Paralleled Linear Amplifiers," J. Audio Eng. Soc., vol. 22, pp. 602-613 (1974 Oct.).

- [3] J. A. Grocock, "Design with Paralleled Transistors for Use with Low Source Resistances," *Wireless World*, pp. 117-118 (1975 Mar.).

- [4] G. Erdi, "Amplifier Techniques for Combining Low-Noise, Precision, and High-Speed Performance," *IEEE J. Solid-State Circuits*, vol. SC-16, pp. 653-661 (1981 Dec.).

LEACH ENGINEERING REPORTS

- [5] T. F. Darling, "Mathematical Noise Modeling and Analysis of Some Popular Preamplifier Circuit Topologies," *J. Audio Eng. Soc.*, vol. 35, pp. 15–23 (1987 Jan./Feb.).

- [6] C. D. Motchenbacher and J. A. Connelly, Low Noise Electronic System Design (Wiley, New York, 1993).

- [7] W. M. Leach, Jr., "Fundamentals of Low-Noise Analog Circuit Design," *Proc. IEEE*, vol. 82, pp. 1515–1538 (1994 Oct.).

- [8] P. R. Gray and R. G. Meyer, Analysis and Design of Analog Integrated Circuits (Wiley, New York, 1993).

- [9] P. E. Allen and R. Holbert, *CMOS Analog Circuit Design* (Holt, Rinehart, and Winston, New York, 1987).